#### Introduction to CMOS VLSI Design

#### Lecture 18: Design for Low Power

**David Harris**

Harvey Mudd College Spring 2004

### Outline

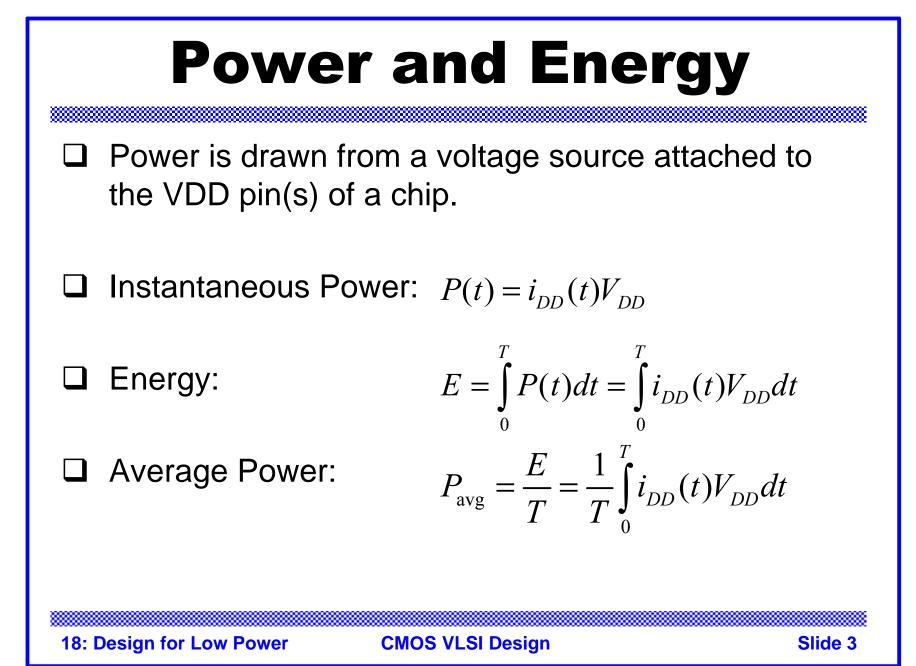

- Power and Energy

- Dynamic Power

- Static Power

- Low Power Design

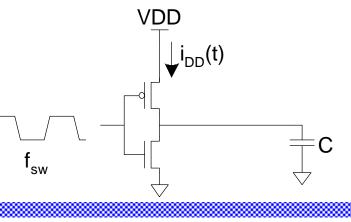

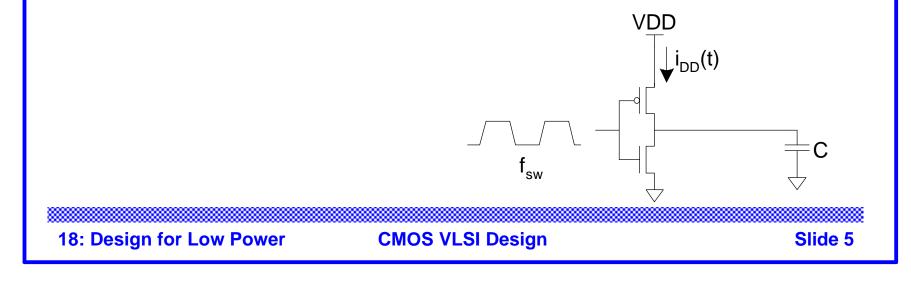

## **Dynamic Power**

- Dynamic power is required to charge and discharge load capacitances when transistors switch.

- One cycle involves a rising and falling output.

- **On rising output, charge**  $Q = CV_{DD}$  **is required**

- On falling output, charge is dumped to GND

- This repeats Tf<sub>sw</sub> times over an interval of T

## **Dynamic Power Cont.**

$P_{\rm dynamic}$

# **Activity Factor**

- □ Suppose the system clock frequency = f

- $\Box$  Let  $f_{sw} = \alpha f$ , where  $\alpha = activity factor$

- If the signal is a clock,  $\alpha = 1$

- If the signal switches once per cycle,  $\alpha = \frac{1}{2}$

- Dynamic gates:

- Switch either 0 or 2 times per cycle,  $\alpha = \frac{1}{2}$

- Static gates:

- Depends on design, but typically  $\alpha = 0.1$

**Dynamic power:**  $P_{\text{dynamic}} = \mathbf{a} C V_{DD}^{2} f$

18: Design for Low Power

# **Short Circuit Current**

- When transistors switch, both nMOS and pMOS networks may be momentarily ON at once

- Leads to a blip of "short circuit" current.

- < 10% of dynamic power if rise/fall times are comparable for input and output

### Example

- 200 Mtransistor chip

- 20M logic transistors

- Average width: 12  $\lambda$

- 180M memory transistors

- Average width: 4  $\lambda$

- 1.2 V 100 nm process

- $C_g = 2 \text{ fF}/\mu m$

# **Dynamic Example**

- □ Static CMOS logic gates: activity factor = 0.1

- Memory arrays: activity factor = 0.05 (many banks!)

- Estimate dynamic power consumption per MHz. Neglect wire capacitance and short-circuit current.

### **Static Power**

- Static power is consumed even when chip is quiescent.

- Ratioed circuits burn power in fight between ON transistors

- Leakage draws power from nominally OFF devices

$$I_{ds} = I_{ds0} e^{\frac{V_{gs} - V_t}{nv_T}} \left[ 1 - e^{\frac{-V_{ds}}{v_T}} \right]$$

$$V_t = V_{t0} - \boldsymbol{h}V_{ds} + \boldsymbol{g}\left(\sqrt{\boldsymbol{f}_s + V_{sb}} - \sqrt{\boldsymbol{f}_s}\right)$$

**18: Design for Low Power**

**CMOS VLSI Design**

Slide 12

# **Ratio Example**

□ The chip contains a 32 word x 48 bit ROM

- Uses pseudo-nMOS decoder and bitline pullups

- On average, one wordline and 24 bitlines are high

- □ Find static power drawn by the ROM

$$-\beta = 75 \ \mu \text{A/V}^2$$

$$-V_{tp} = -0.4V$$

# Leakage Example

- The process has two threshold voltages and two oxide thicknesses.

- □ Subthreshold leakage:

- 20 nA/ $\mu m$  for low  $V_t$

- 0.02 nA/ $\mu m$  for high  $V_t$

- Gate leakage:

- 3 nA/ $\mu m$  for thin oxide

- 0.002 nA/ $\mu m$  for thick oxide

- Memories use low-leakage transistors everywhere

- ☐ Gates use low-leakage transistors on 80% of logic

# Leakage Example Cont.

**G** Estimate static power:

**18: Design for Low Power**

**CMOS VLSI Design**

Slide 16

### Low Power Design

- □ Reduce dynamic power

- α:

- C:

- $-V_{DD}$ :

- f:

- Reduce static power